# Advance Information

# **Configurable Octal Serial Switch** with Serial Peripheral Interface I/O

The 33880 device is an eight output hardware configurable high side/low side switch with 8-bit serial input control. Two of the outputs may be controlled directly via microprocessor for PWM applications. The 33880 incorporates SMARTMOS™ technology, with CMOS logic, bipolar/MOS analog circuitry, and DMOS power MOSFETs. The 33880 controls various inductive or incandescent loads by directly interfacing with a micro controller. The circuit's innovative monitoring and protection features include: very low standby currents; cascade fault reporting; internal +40 V clamp voltage for low side configuration; -20 V high side configuration; output specific diagnostics; and independent shutdown of output.

#### Features

- Designed to operate 5.5 V < V<sub>PWR</sub> < 24.5 V</li>

- 8-Bit SPI for Control and Fault Reporting, 3.3 V/5.0 V Compatible

- Outputs are current limited (0.8 A to 2 A) to Drive Incandescent Lamps •

- Output voltage Clamp, +45 V (low side) and -20 V (high side) During Inductive Switching

- Internal Reverse Battery Protection on VPWR

- Loss of Ground or Supply Will Not Energize Loads or Damage IC •

- Maximum 5 µA I<sub>PWR</sub> Standby Current at 13.0 V V<sub>PWR</sub> •

- R<sub>DS(ON)</sub> of 0.55Ω at 25°C Typical ٠

- Short Circuit Detect and Current Limit with Automatic Retry

- Independent Over Temperature Protection

#### ORDERING INFORMATION

| Device     | Temperature<br>Range (T <sub>A</sub> ) | Package    |

|------------|----------------------------------------|------------|

| PC33880DW  | -40°C to 125°C                         | 28 Ld SOIC |

| PC33880DWB | -40°C to 125°C                         | 32 Ld SOIC |

This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

SUNSTAR自动化 http://www.sensor-ic.com/ TEL: 0755-83376489 FAX:0755-8 © Motorola, Inc. 2002

33880

**CONFIGURABLE OCTAL SERIAL**

SWITCH WITH SERIAL

PERIPHERAL INTERFACE

Figure 1. 33880 Simplified Block Diagram

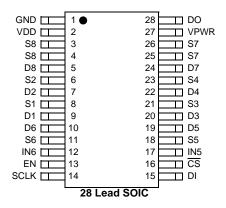

#### **PIN FUNCTION DESCRIPTON 28 SOIC**

| 28-Lead<br>SOIC | PIN NAME        | DESCRIPTION                                                                                                 |  |  |  |  |

|-----------------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN             |                 |                                                                                                             |  |  |  |  |

| 1               | GND             | Digital ground.                                                                                             |  |  |  |  |

| 2               | V <sub>DD</sub> | Logic supply voltage. Logic supply must be switched off for low current mode (V <sub>DD</sub> below 3.9 V). |  |  |  |  |

| 3               | S8              | Output eight MOSFET source pin.                                                                             |  |  |  |  |

| 4               | S8              | Output eight MOSFET source pin.                                                                             |  |  |  |  |

| 5               | D8              | Output eight MOSFET drain pin.                                                                              |  |  |  |  |

| 6               | S2              | Output two MOSFET source pin.                                                                               |  |  |  |  |

| 7               | D2              | Output two MOSFET drain pin.                                                                                |  |  |  |  |

| 8               | S1              | Output one MOSFET source pin.                                                                               |  |  |  |  |

| 9               | D1              | Output one MOSFET drain pin.                                                                                |  |  |  |  |

| 10              | D6              | Output six MOSFET drain pin.                                                                                |  |  |  |  |

| 11              | S6              | Output six MOSFET source pin.                                                                               |  |  |  |  |

| 12              | IN6             | PWM direct control input pin for output 6. IN6 is "OR" with SPI bit.                                        |  |  |  |  |

| 13              | EN              | Enable input. Allows control of outputs. Active high.                                                       |  |  |  |  |

| 14              | SCLK            | SPI control clock input pin.                                                                                |  |  |  |  |

| 15              | DI              | SPI control data input pin from MCU to the 33880. Logic 1 activates output.                                 |  |  |  |  |

| 16              | CS              | SPI control chip select input pin from MCU to the 33880. Logic 0 allows data to be transferred in.          |  |  |  |  |

| 17              | IN5             | PWM direct control input pin for output 5. IN5 is "OR" with SPI bit.                                        |  |  |  |  |

| 18              | S5              | Output five MOSFET source pin.                                                                              |  |  |  |  |

| 19              | D5              | Output five MOSFET drain pin.                                                                               |  |  |  |  |

| 20              | D3              | Output three MOSFET drain pin.                                                                              |  |  |  |  |

| 21              | S3              | Output three MOSFET source pin.                                                                             |  |  |  |  |

| 22              | D4              | Output four MOSFET drain pin.                                                                               |  |  |  |  |

#### **PIN FUNCTION DESCRIPTON 28 SOIC**

| 28-Lead<br>SOIC | PIN NAME         | DESCRIPTION                                                                                             |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------|

| PIN             |                  |                                                                                                         |

| 23              | S4               | Output four MOSFET source pin.                                                                          |

| 24              | D7               | Output seven MOSFET drain pin.                                                                          |

| 25              | S7               | Output seven MOSFET source pin.                                                                         |

| 26              | S7               | Output seven MOSFET source pin.                                                                         |

| 27              | V <sub>PWR</sub> | Power supply pin to the 33880. $V_{PWR}$ has internal reverse battery protection.                       |

| 28              | DO               | SPI control data output pin from the 33880 to the MCU. DO= 0 no fault, DO= 1 specific output has fault. |

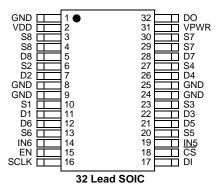

### **PIN FUNCTION DESCRIPTON 32 SOIC**

| SOIC-32 |                 | DECODIDION                                                                                                  |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------|

| PIN     | PIN NAME        | DESCRIPTION                                                                                                 |

| 1       | GND             | Digital ground.                                                                                             |

| 2       | V <sub>DD</sub> | Logic supply voltage. Logic supply must be switched off for low current mode (V <sub>DD</sub> below 3.9 V). |

| 3       | S8              | Output eight MOSFET source pin.                                                                             |

| 4       | S8              | Output eight MOSFET source pin.                                                                             |

| 5       | D8              | Output eight MOSFETdrain pin.                                                                               |

| 6       | S2              | Output two MOSFET source pin.                                                                               |

| 7       | D2              | Output two MOSFET drain pin.                                                                                |

| 8       | GND             | Thermal enhanced ground pin.                                                                                |

| 9       | GND             | Thermal enhanced ground pin.                                                                                |

| 10      | S1              | Output one MOSFET source pin.                                                                               |

| 11      | D1              | Output one MOSFET drain pin.                                                                                |

| 12      | D6              | Output six MOSFETdrain pin.                                                                                 |

| 13      | S6              | Output six MOSFET source pin.                                                                               |

| 14      | IN6             | PWM direct control input pin for output 6. IN6 is "AND" with SPI bit.                                       |

| 15      | EN              | Enable input. Allows control of outputs. Active high.                                                       |

| 16      | SCLK            | SPI control clock input pin.                                                                                |

| 17      | DI              | SPI control data input pin from MCU to the 33880. Logic 1 activates output.                                 |

| 18      | CS              | SPI control chip select input pin from MCU to the 33880. Logic 0 allows data to be transferred in.          |

| 19      | IN5             | PWM direct control input pin for output 5. IN5 is "AND" with SPI bit.                                       |

| 20      | S5              | Output five MOSFET source pin.                                                                              |

| 21      | D5              | Output five MOSFET drain pin.                                                                               |

| 22      | D3              | Output three MOSFET drain pin.                                                                              |

# SUNSTAR传感与控制 http://www.sensor-ic.com/ TEL:0755-83376549 FAX:0755-83376182 E-MAIL:szss20@163.com PIN FUNCTION DESCRIPTON 32 SOIC

| SOIC-32 | PIN NAME         | DESCRIPTION                                                                                             |  |  |  |  |

|---------|------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN     |                  | DESCRIPTION                                                                                             |  |  |  |  |

| 23      | S3               | Output three MOSFET source pin.                                                                         |  |  |  |  |

| 24      | GND              | Thermal enhanced ground pin.                                                                            |  |  |  |  |

| 25      | GND              | Thermal enhanced ground pin.                                                                            |  |  |  |  |

| 26      | D4               | Output four MOSFET drain pin.                                                                           |  |  |  |  |

| 27      | S4               | Output four MOSFET source pin.                                                                          |  |  |  |  |

| 28      | D7               | Output seven MOSFET drain pin.                                                                          |  |  |  |  |

| 29      | S7               | Output seven MOSFET source pin.                                                                         |  |  |  |  |

| 30      | S7               | Output seven MOSFET source pin.                                                                         |  |  |  |  |

| 31      | V <sub>PWR</sub> | Power supply pin to the 33880. $V_{PWR}$ has internal reverse battery protection.                       |  |  |  |  |

| 32      | DO               | SPI control data output pin from the 33880 to the MCU. DO= 0 no fault, DO= 1 specific output has fault. |  |  |  |  |

| Rating                                                                      | Symbol             | Value         | Unit            |

|-----------------------------------------------------------------------------|--------------------|---------------|-----------------|

| V <sub>DD</sub> Supply Voltage (Note1)                                      | V <sub>DD</sub>    | -0.3 to 7.0   | $V_{DC}$        |

| CS, DI, DO, SCLK, IN5, IN6, and EN (Note1)                                  | _                  | -0.3 to 7.0   | V <sub>DC</sub> |

| V <sub>PWR</sub> Supply Voltage (Note1)                                     | V <sub>PWR</sub>   | -16 to 50     | V <sub>DC</sub> |

| Drain 1 - 8 (5.0 mA ≤ I <sub>OUT</sub> ≤ 0.3 A) (Note2)                     | _                  | -18 to 40     | V <sub>DC</sub> |

| Source 1 - 8 (5.0 mA ≤ I <sub>OUT</sub> ≤ 0.3 A) (Note3)                    | _                  | -28 to 40     | V <sub>DC</sub> |

| Output Voltage Clamp Low Side Drive (Note4)                                 | V <sub>OC</sub>    | 40 to 55      | V <sub>DC</sub> |

| Output Voltage Clamp High Side Drive (Note4)                                | V <sub>OC</sub>    | -15 to -25    | V <sub>DC</sub> |

| Output Clamp Energy (Note5)                                                 | E <sub>CLAMP</sub> | 50            | mJ              |

| ESD Voltage                                                                 |                    |               |                 |

| Human Body Model (Note6)                                                    | V <sub>ESD1</sub>  | 2000          | V               |

| Machine Model (Note7)                                                       | V <sub>ESD2</sub>  | 200           | V               |

| Storage Temperature                                                         | T <sub>STG</sub>   | -55° to +150° | °C              |

| Operating Case Temperature                                                  | T <sub>C</sub>     | -40° to +125° | °C              |

| Operating Junction Temperature                                              | TJ                 | -40° to +150° | °C              |

| Maximum Junction Temperature                                                | _                  | -40° to +150° | °C              |

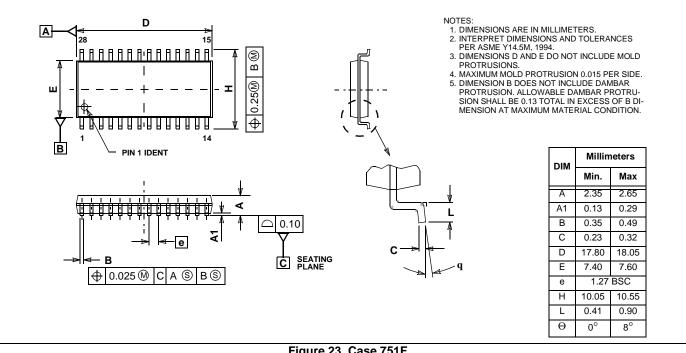

| Power Dissipation 28-SOIC, Case 751F ( $T_a = 25^{\circ}C$ ) (Note8)        | PD                 | 1.3           | W               |

| Thermal Resistance, Junction-to-Ambient Plastic Package 28 SOIC, Case 751F  | R <sub>θJA</sub>   | 94            | °C/W            |

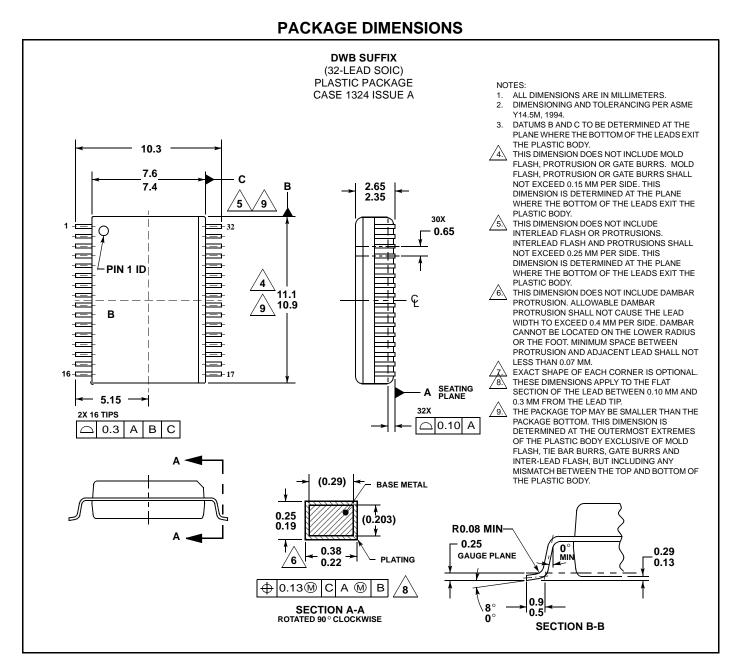

| Power Dissipation 32-SOIC, Case 1324 ( $T_a = 25^{\circ}C$ ) (Note8)        | PD                 | 1.7           | W               |

| Thermal Resistance, Junction-to-Ambient, Plastic Package 32SOIC, Case 1324, | RθJA               | 70            | °C/W            |

| Thermal Resistance Junction to thermal ground leads.                        | RθJL               | 18            |                 |

Notes:

1. Exceeding these limits may cause malfunction or permanent damage to the device.

2. Configured as Low Side Driver with 300 mA load as current limit.

3. Configured as High Side Driver with 300 mA load as current limit.

4. With outputs OFF and 10 mA of test current for low side drive, 30 mA test current for high side drive.

5. Maximum output clamp energy capability at 150°C junction temperature using single non-repetitive pulse method.

6. ESD1 testing is performed in accordance with the Human Body Model ( $C_{Zap} = 100 \text{ pF}, R_{Zap} = 1500 \Omega$ ).

7. ESD2 testing is performed in accordance with the Machine Model ( $C_{Zap}$  = 200 pF,  $R_{Zap}$  = 0  $\Omega$ ).

8. Maximum power dissipation with no heat sink used.

#### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>C</sub>  $\leq$  125°C, unless otherwise noted. Typical values, where applicable, reflect the parameter's approximate average value with V<sub>PWR</sub> = 13 V, T<sub>A</sub> = 25°C

| Characteristic                                                     | Symbol                     | Min  | Тур  | Мах  | Unit |

|--------------------------------------------------------------------|----------------------------|------|------|------|------|

| Power Input                                                        |                            |      |      |      |      |

| Supply Voltage Range                                               |                            |      |      |      |      |

| Fully Operational                                                  | V <sub>PWR(fo)</sub>       | 5.5  | —    | 24.5 | V    |

| Supply Current                                                     | I <sub>PWR(on)</sub>       | _    | 8.0  | 14   | mA   |

| Sleep State Supply Current (V <sub>DD</sub> and EN $\leq$ 0.5 V)   | I <sub>PWR(ss)</sub>       | _    | 2.0  | 5.25 | μA   |

| V <sub>PWR</sub> = 16.0 V                                          |                            | —    | —    | 25   |      |

| Over Voltage Shutdown                                              | V <sub>OV</sub>            | 25   | 27   | 30   | V    |

| Over Voltage Shutdown Hysteresis                                   | V <sub>OV(hys)</sub>       | 0.2  | 0.8  | 2.5  | V    |

| Logic Supply Voltage                                               | V <sub>DD</sub>            | 4.75 | _    | 5.25 | V    |

| Logic Supply Current                                               | I <sub>DD</sub>            | 0.5  | 2.6  | 4.0  | mA   |

| Logic Supply Under Voltage Lockout Threshold                       | V <sub>DD(unvol)</sub>     | 3.9  | 4.3  | 4.6  | V    |

| Logic Supply Under Voltage Hysteresis                              | V <sub>DD(unvol-hys)</sub> | 100  | 150  | 300  | mV   |

| Power Output                                                       |                            |      |      |      |      |

| Drain-to-Source ON Resistance                                      |                            |      |      |      |      |

| (I <sub>OUT</sub> = 0.250 A, T <sub>J</sub> = 125°C)               | R <sub>DS (on)</sub>       | —    | 0.75 | 1.1  |      |

| (I <sub>OUT</sub> = 0.250 A, T <sub>J</sub> = 25°C)                |                            | —    | 0.55 | 0.85 | Ω    |

| (I <sub>OUT</sub> = 0.250 A, T <sub>J</sub> = -40°C)               |                            | —    | 0.45 | 0.80 |      |

| Output Self Limiting Current High Side and Low Side Configurations | I <sub>OUT(LIM)</sub>      | 0.8  | 1.4  | 2.0  | A    |

| Output Fault Detect Threshold (Note9)(Note10)                      |                            |      |      |      |      |

| Outputs Programmed Off                                             | V <sub>OUTth(F)</sub>      | 1.0  | _    | 3.0  | V    |

| Output Off Open Load Detect Current (Note9)                        |                            |      |      |      |      |

| Outputs Programmed OFF                                             | I <sub>OCO</sub>           | 0.30 | 0.55 | 0.9  | mA   |

| Output Clamp Voltage Low Side Drive (I <sub>D</sub> = 10 mA)       | V <sub>OC(LSD)</sub>       | 40   | 45   | 55   | V    |

| Output Clamp Voltage High Side Drive (I <sub>S</sub> = -30 mA)     | V <sub>OC(HSD)</sub>       | -15  | -20  | -25  | V    |

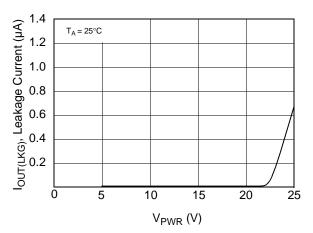

| Output Leakage Current High Side and Low Side Configuration        | I <sub>OUT(LKG)</sub>      |      |      |      | μA   |

| $(V_{DD} = 0 V, V_{DS} = 16 V)$                                    | 001(210)                   | —    | _    | 7.0  |      |

| Over Temperature Shutdown (Note10)                                 | T <sub>LIM</sub>           | 155  | _    | 185  | °C   |

| Over Temperature Shutdown Hysteresis (Note10)                      | T <sub>LIM(HYST)</sub>     | 5.0  | 10   | 15   | °C   |

Notes:

9. Output Fault Detect Thresholds with outputs programmed OFF. Output fault detect threshold are the same for output open and shorts.

10. This parameter is guaranteed by design, but not production tested.

#### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>C</sub>  $\leq$  125°C, unless otherwise noted. Typical values, where applicable, reflect the parameter's approximate average value with V<sub>PWR</sub> = 13 V, T<sub>A</sub> = 25°C

#### **Digital Interface**

| Input Logic Voltage Thresholds (Note11)                            | VINLOGIC                  | 0.8                   | —  | 2.2             | V  |

|--------------------------------------------------------------------|---------------------------|-----------------------|----|-----------------|----|

| IN5, IN6, EN Input Logic Current (IN5,IN6,EN = 0 V)                | I <sub>IIN5,IN6,EN</sub>  | -10                   | _  | 10              | μA |

| IN5, IN6, EN Pull-Down Current (0.8 V to V <sub>DD</sub> )         | I <sub>IIN5,IN6,EN</sub>  | 30                    | 45 | 100             | μΑ |

| SCLK, DI, Tri-state DO Input (0 V to V <sub>DD</sub> )             | I <sub>SCK,SI,TriSO</sub> | -10                   | _  | 10              | μA |

| CS Input Current (CS = V <sub>DD</sub> )                           | I <sub>ICS</sub>          | -10                   | _  | 10              | μA |

| CS Pull-Up Current (CS = 0 V)                                      | I <sub>ICS</sub>          | -30                   | _  | -100            | μA |

| DO High State Output Voltage (I <sub>DO-HIGH</sub> = -200 μA)      | V <sub>DOHIGH</sub>       | V <sub>DD</sub> - 0.8 | —  | V <sub>DD</sub> | V  |

| DO Low State Output Voltage (I <sub>DO-HIGH</sub> = 1.6 mA)        | V <sub>DOLOW</sub>        | _                     | _  | 0.4             | V  |

| Input Capacitance on SCLK, DI, Tri-state DO, IN5, IN6, EN (Note12) | C <sub>IN</sub>           | —                     | _  | 20              | pF |

Notes:

11. Upper and lower logic threshold voltage levels apply to DI, CS, SCLK, IN5, IN6, EN.

12. This parameter is guaranteed by design, but not production tested.

#### DYNAMIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>C</sub>  $\leq$  125°C, unless otherwise noted. Typical values, where applicable, reflect the parameter's approximate average value with V<sub>PWR</sub> = 13 V, T<sub>A</sub> = 25°C

| Characteristic                                                            | Symbol                | Min | Тур | Max | Units |

|---------------------------------------------------------------------------|-----------------------|-----|-----|-----|-------|

| Power Output Timing                                                       |                       |     |     |     |       |

| Output Rise Time Low Side Configuration (RL = $620\Omega$ ) (Note13)      | t <sub>R</sub>        | 0.1 | 0.5 | 1.0 | V/µs  |

| Output Fall Time Low Side Configuration (RL = 620 $\Omega$ ) (Note13)     | t <sub>F</sub>        | 0.1 | 0.5 | 1.0 | V/µs  |

| Output Rise Time High Side Configuration (RL = $620\Omega$ ) (Note13)     | t <sub>R</sub>        | 0.1 | 0.3 | 1.0 | V/µs  |

| Output Fall Time High Side Configuration (RL = 620 $\Omega$ ) (Note13)    | t <sub>F</sub>        | 0.1 | 0.3 | 1.0 | V/µs  |

| Output Turn ON Delay Time, High Side and Low Side Configuration (Note14)  | t <sub>DLY(on)</sub>  | 1.0 | 15  | 50  | μs    |

| Output Turn OFF Delay Time, High Side and Low Side Configuration (Note14) | t <sub>DLY(off)</sub> | 1.0 | 30  | 100 | μs    |

| Output Fault Delay Time (Note15)                                          | t <sub>FAULT</sub>    | 100 | —   | 300 | μs    |

Notes::

13. Output Rise and Fall time respectively measured across a 620Ω resistive load at 10 to 90 percent and 90 to 10percent voltage points.

14. Output turn ON and OFF delay time measured from 50 percent rising edge of CS to 90 and 10 percent of initial voltage.

15. Duration of fault before fault bit is set. Duration between access times must be greater than 300 µS to read faults.

#### DYNAMIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions of 4.75 V  $\leq$  V<sub>DD</sub>  $\leq$  5.25 V, 9.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>C</sub>  $\leq$  125°C, unless otherwise noted. Typical values, where applicable, reflect the parameter's approximate average value with V<sub>PWR</sub> = 13 V, T<sub>A</sub> = 25°C

| Characteristic                                                                            | Symbol                 | Min | Тур | Мах | Units |  |  |

|-------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|-------|--|--|

| Digital Interface Timing                                                                  |                        |     |     |     |       |  |  |

| Recommended Frequency of SPI Operation                                                    |                        | _   | 4.0 | 6.0 | MHz   |  |  |

| Required Low State Duration on $V_{DD}$ for Reset ( $V_{DD} \le 0.2 \text{ V}$ ) (Note16) | t <sub>RESET</sub>     |     | 4.0 | 10  | μs    |  |  |

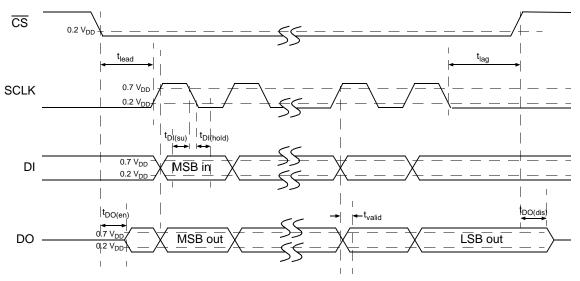

| Falling Edge of $\overline{CS}$ to Rising Edge of SCLK (Required Setup Time)              | t <sub>LEAD</sub>      | 100 | —   | _   | ns    |  |  |

| Falling Edge of SCLK to Rising Edge of CS (Required Setup Time)                           | t <sub>LAG</sub>       | 50  | _   | _   | ns    |  |  |

| DI to Falling Edge of SCLK (Required Setup Time)                                          | t <sub>DI(su)</sub>    | 16  | _   | _   | ns    |  |  |

| Falling Edge of SCLK to DI (Required Hold Time)                                           | t <sub>DI(HOLD</sub> ) | 20  | _   | _   | ns    |  |  |

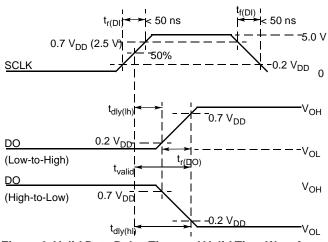

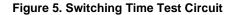

| DI, CS, SCLK Signal Rise Time (Note17)                                                    | t <sub>r(DI)</sub>     | —   | 5   | _   | ns    |  |  |

| DI, CS, SCLK Signal Fall Time (Note17)                                                    | t <sub>f(DI)</sub>     | —   | 5   | _   | ns    |  |  |

| Time from Falling Edge of $\overline{CS}$ to DO Low Impedance (Note18)                    | t <sub>DO(EN)</sub>    | _   | _   | 55  | ns    |  |  |

| Time from Rising Edge of $\overline{CS}$ to DO High Impedance (Note19)                    | t <sub>DO(DIS)</sub>   | _   | —   | 55  | ns    |  |  |

| Time from Rising Edge of SCLK to DO Data Valid (Note20)                                   | t <sub>VALID</sub>     | —   | 25  | 55  | ns    |  |  |

Notes:

16. This parameter is guaranteed by design, but not production tested.

17. Rise and Fall time of incoming DI, CS, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

18. Time required for output status data to be available for use at DO pin.

19. Time required for output status data to be terminated at DO pin

20. Time required to obtain valid data out from DO following the rise of SCLK.

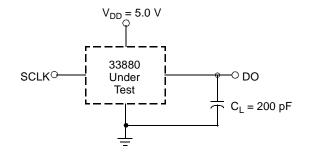

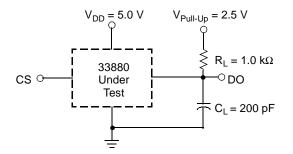

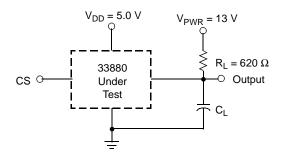

NOTE: CL represents the total capacitance of the test

#### Figure 3. Valid Data Delay Time and Valid Time Test Circuit

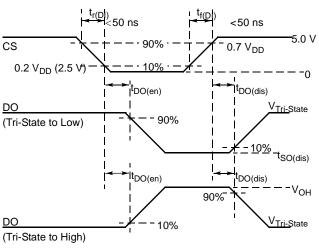

Figure 6. Valid Data Delay Time and Valid Time Waveforms

NOTE:  $C_L$  represents the total capacitance of the test fixture and probe.

#### Figure 4. Enable and Disable Time Test Circuit

NOTE:  $C_L$  represents the total capacitance of the test fixture and probe.

Figure 7. Enable and Disable Time Waveforms

## **SPI** Definition

On each SPI communication, an 8-bit command word is sent to the 33880 and 8-bit fault word is received from the 33880. The MSB is sent and received first

Command Register Definition:

0 = Output Commanded OFF

1 = Output Commanded ON

Fault Register Definition:

0 = No Fault at Output

1 = Output Short to Bat, Short to GND, Open Load, or TLIM

| MSB   |       |       |       |       |       |       | LSB   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OUT 8 | OUT 7 | OUT 6 | OUT 5 | OUT 4 | OUT 3 | OUT 2 | OUT 1 |

#### **Fault Operation**

#### Serial Output (DO) Pin Reports

| Over Temperature           | Fault reported by Serial Output (DO) pin.                        |

|----------------------------|------------------------------------------------------------------|

| Over Current               | DO pin reports short to battery/supply or over current condition |

| Output ON Open Load Fault  | Not Reported                                                     |

| Output OFF Open Load Fault | DO pin reports output OFF open load condition                    |

#### **Device Shutdowns**

| Over Voltage     | Total device shutdown at $V_{PWR}$ = 25-30 V. Resumes normal operation with proper voltage. All outputs |

|------------------|---------------------------------------------------------------------------------------------------------|

|                  | assuming the previous state upon recovery from overvoltage.                                             |

| Over Temperature | Only the output experiencing an over temperature shuts down. Output assumes previous state upon         |

|                  | recovery from over temperature.                                                                         |

# SYSTEM APPLICATION INFORMATION

## **CIRCUIT DESCRIPTION**

#### Introduction

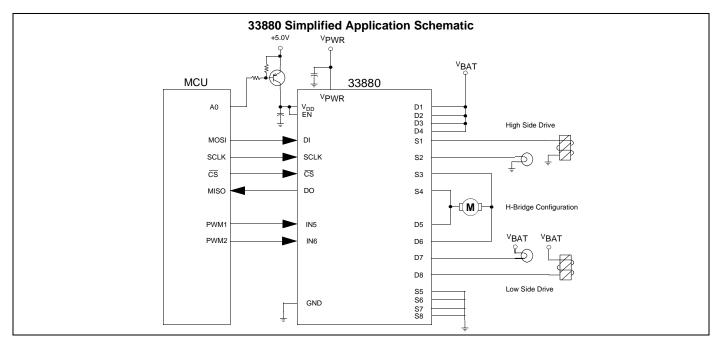

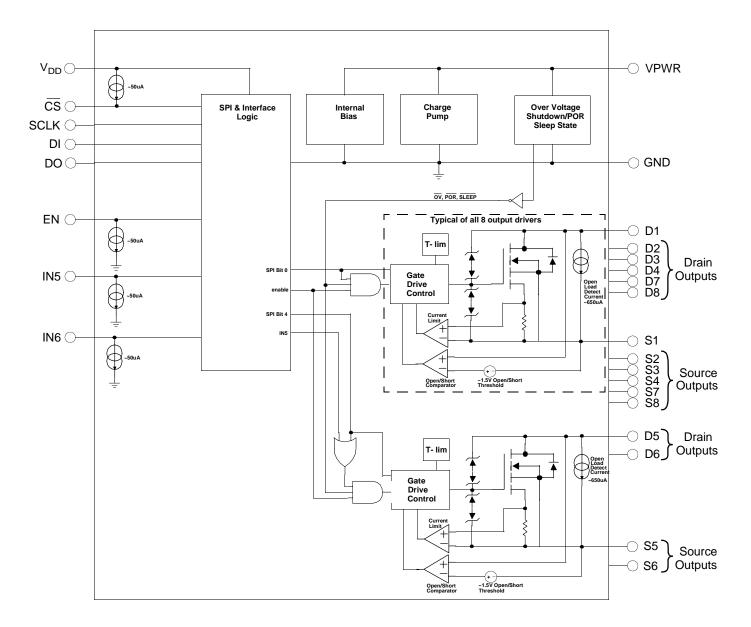

The 33880 is an eight-output hardware configurable power switch with 8-bit serial control. The 33880 incorporates SMARTMOS<sup>™</sup> 5 technology with CMOS logic, bipolar/MOS analog circuitry, and independent double diffused DMOS power output transistors. Many benefits are realized as a direct result of using this mixed technology. A simplified block diagram of the 33880 is shown in Figure 1.

The 33880 device uses high efficiency updrain power DMOS output transistors exhibiting low drain to source ON resistance values (RDS(on) <= 0.55  $\Omega$  at 25°C) and dense CMOS control logic. All outputs have independent voltage clamps to provide fast inductive turn-off and transient protection. Operational bias currents of less than 4mA on V<sub>DD</sub> and 12 mA on V<sub>PWR</sub> with any combination of outputs ON are a direct result of using SMARTMOS<sup>TM</sup> 5 technology.

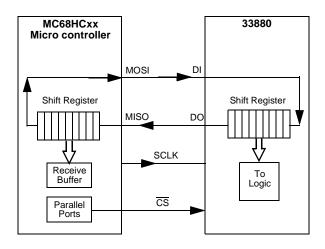

In operation, the 33880 functions as an eight-output serial switch serving as a micro controller (MCU) bus expander and buffer with fault management and fault reporting features. In doing so, the device directly relieves the MCU of the fault management functions. This device directly interfaces to an MCU using a Serial Peripheral Interface (SPI) for control and diagnostic readout. Figure 9 illustrates the basic SPI configuration between an MCU and one 33880.

#### Figure 9. SPI Interface with Microcontroller

All inputs are compatible with 5.0 V and 3.3 V CMOS logic levels and incorporate positive logic. Whenever an input is programmed to a logic low state (<0.8 V) the corresponding output will be OFF. Conversely, whenever an input is programmed to a logic high state (>2.2 V), the output being controlled will be ON. Diagnostics are treated in a similar manner. Outputs with a fault will feedback (via DO) to the micro as a logic one while normal operating outputs will provide a logic zero.

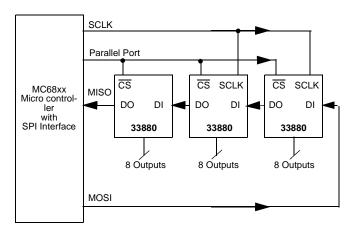

Figure 10 illustrates the Daisy Chain configuration using the 33880. Data from the MCU is clocked daisy chain through each device while the Chip Select ( $\overline{CS}$ ) bit is commanded low by the MCU. During each clock cycle output status from the daisy chain, the 33880 is being transferred to the MCU via the Master In Slave Out (MISO) line. On rising edge of  $\overline{CS}$  data stored in the input register is then transferred to the output driver.

Figure 10. 33880 SPI System Daisy Chain

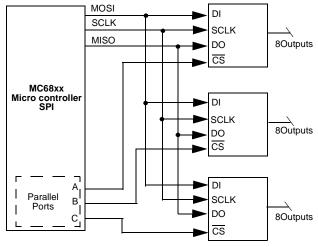

Multiple 33880 devices can be controlled in a parallel input fashion using the SPI, see Figure 11. This figure illustrates possible 24 loads being controlled by three dedicated parallel MCU ports used for chip select.

Figure 11. Parallel Input SPI Control

# PIN FUNCTIONAL DESCRIPTION

# CS Pin

The system MCU selects the 33880 to communicate through the use of the  $\overline{CS}$  pin. Whenever the pin is in a logic low state, data can be transferred from the MCU to the 33880 device and vice versa. Clocked-in data from the MCU is transferred from the 33880 shift register and latched into the power outputs <u>on</u> the rising edge of the  $\overline{CS}$  signal. On the falling edge of the  $\overline{CS}$ signal, output status information is transferred from the power outputs status register into the device's shift register. The falling edge of  $\overline{CS}$  enables the DO output driver. Whenever the  $\overline{CS}$  pin goes to a logic low state, the DO pin output is enabled, thereby allowing information to be transferred from the 33880 to the MCU. To avoid any spurious data, it is essential the high-to-low transition of the  $\overline{CS}$  signal occur only when SCLK is in a logic low state.

## SCLK Pin

The system clock pin (SCLK) clocks the internal shift registers of the 33880. The serial data input (DI) is latched into the input shift register on the falling edge of the SCLK. The serial data output pin (DO) shifts data out of the shift register on the rising edge of the SCLK signal. False clocking of the shift register must be avoided to guarantee validity of data. It is essential the SCLK pin be in a logic low state whenever chip select pin ( $\overline{CS}$ ) makes any transition. For this reason, it is recommended the SCLK pin is commanded to a logic low state when the device is not accessed ( $\overline{CS}$  in logic high state). When the  $\overline{CS}$  is in a logic high state, any signal at the SCLK and DI pin is ignored and the DO is tri-stated (high impedance).

## DI Pin

This pin is used for serial instruction data input. DI information is latched into the input register on the falling edge of SCLK. A logic high state present on DI will program a specific output on. The specific output will turn on with the rising edge of the  $\overline{CS}$  signal. Conversely, a logic low state present on the DI pin will program the output *off*. The specific output will turn *off* with the rising edge of the  $\overline{CS}$  signal. To program the eight outputs of the 33880 device *on* or *off*, enter the DI pin beginning with Output 8, followed by Output 7, Output 6, and so on to Output 1. For each falling edge of the SCLK while  $\overline{CS}$  is logic low, a data bit instruction (*on* or *off*) is loaded into the shift register per the data bit DI state. Eight bits of entered information fills the shift register. To preserve data integrity, do not transition DI as SCLK transitions from a high to low logic state.

## DO Pin

The serial data output (DO) pin is the output from the shift register. The DO pin remains tri-state until the  $\overline{CS}$  pin goes to a logic low state. All faults on the 33880 device are reported as logic one through the DO data pin. Regardless of the configuration of the driver, open loads, and shorted loads are

reported as logic one. Conversely, normal operating outputs with non-faulted loads are reported as logic zero. The first positive transition of SCLK will make output eight status available on DO pin. Each successive positive clock will make the next output status available. The DI/DO shifting of data follows a first-in-first-out protocol with both input and output words transferring the most significant bit (MSB) first.

## EN Pin

The ENABLE pin on the 33880 device either enables or disables the internal charge pump. The enable pin must be high for this device to enhance the gates of the output drivers, perform fault detection, and reporting. Active outputs during a low transition of the EN pin will become active again when the EN transitions high. If this feature is not required, it is recommended the EN pin be connected to  $V_{DD}$ .

## IN5 and IN6 Pins

The IN5 and IN6 pins command inputs allowing outputs five and six to be used in PWM applications. IN5 and IN6 pins are ORed with the SPI communication input. For SPI control of output five and six, the IN5 and IN6 pins should be grounded or held low by the microprocessor. In the same manor, when using the PWM feature the SPI port must command the outputs off. Maximum PWM frequency for each output is 2 kHz.

## $\mathbf{V}_{\text{DD}}$ Pin

The V<sub>DD</sub> pin supplies logic power to the 33880 device and is used for power-on reset (POR). To achieve low standby current on V<sub>PWR</sub> supply, power must be removed from the V<sub>DD</sub> pin. The device will be in reset with all drivers off when V<sub>DD</sub> is below 3.9 V<sub>DC</sub>.

## D1 to D8 Pins

The D1 to D8 pins are the open drain outputs of the 33880. For High Side Drive configurations the Drain pins are connected to battery supply. In Low Side Drive configurations the Drain pins are connected to the low side of the load. All outputs may be configured individually as desired. When Low Side Drive is used the 33880 limit the positive transient for inductive loads to 45 V.

## S1 to S8 Pins

The S1 to S8 pins are the source outputs of the 33880. For High Side Drive configurations the Source pins are connected directly to the load. In Low Side Drive configurations the Source is connected to ground. All outputs may be configured individually as desired. When High Side drive is used, the 33880 will limit the negative transient for inductive loads to -20 volts.

Figure 12. Data Transfer Timing

#### **Power Consumption**

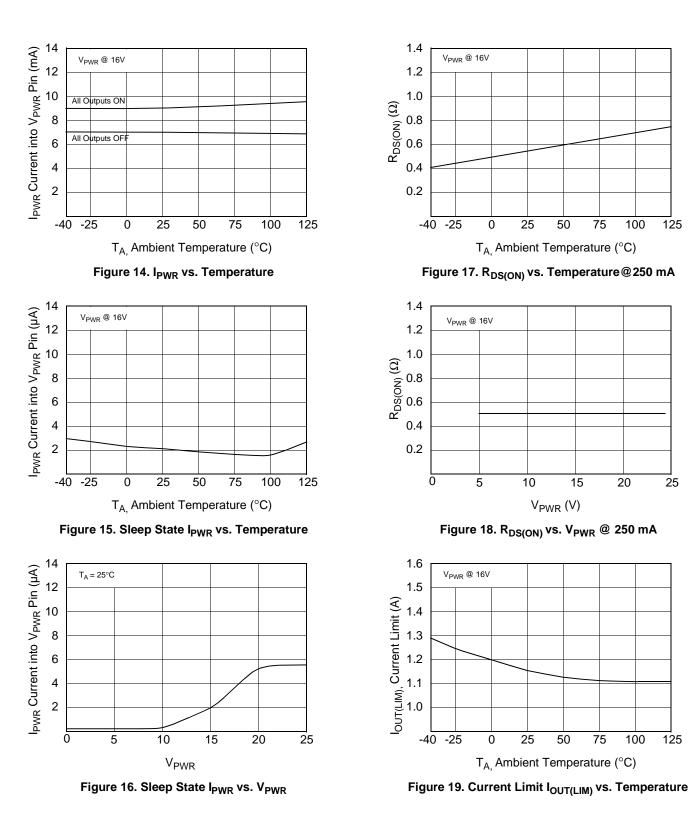

The 33880 device has been designed with one sleep and one operational mode. In the sleep mode ( $V_{DD} \le 2.0$  V) the current consumed by  $V_{PWR}$  pin is less than 25 µA. To place the 33880 in the sleep mode, turn all outputs off, then remove power from  $V_{DD}$  and the EN (enable) input pin. Prior to removing power from the device, it is recommended all control inputs from the micro are low. During normal operation, 4 mA will be drawn from the  $V_{DD}$  supply and 12 mA from the  $V_{PWR}$  supply.

## **Paralleling of Outputs**

Using MOSFETS as output switches allows the connection of any combination of outputs together.  $R_{DS(on)}$  of MOSFETs have an inherent positive temperature coefficient providing balanced current sharing between outputs without destructive operation. The device can even be operated with all outputs tied together. This mode of operation may be desirable in the event the application requires lower power dissipation or the added capability of switching higher currents. Performance of parallel operation results in a corresponding decrease in  $R_{DS(on)}$  while the outputs OFF open load detect currents and the output current limits increase correspondingly (by a factor of eight if all outputs are paralleled). Paralleling outputs from two or more different IC devices is possible but not recommended.

#### **Fault Logic Operation**

Fault logic of the 33880 device has been greatly simplified over other devices using SPI communications. As command word one is being written into the shift register, a fault status word is being simultaneously written out and received by the MCU. Regardless of the configuration, with no outputs faulted, all status bits being received by the MCU will be zero. When outputs are faulted (off state open circuit or on state short circuit/over temperature), the status bits being received by the MCU will be one. The distinction between open circuit fault and short/over temperature is completed via the command word. For example, when a zero command bit is sent and a one fault is received in the following word, the fault is open/short to battery for high side drive or open/short to ground for low side drive. In the same manor when a one command bit is sent and a one fault is received in the following word the fault is a short to ground/over temperature for high side drive or short to battery/over temperature for low side drive. The timing between two write words must be greater than 300  $\mu$ S to allow adequate time to sense and report the proper fault status.

## **SPI Integrity Check**

It is recommended to check the integrity of the SPI communication with the initial power-up of the V<sub>DD</sub> and EN pins. After initial system start-up or reset, the MCU will write one, 16 bit pattern to the 33880. The first eight bits read by the MCU will be the fault status of the outputs while the second eight bits will be the first byte of the bit pattern. By the MCU receiving the same bit pattern it sent, bus integrity is confirmed. Please note

the second byte the MCU sends to the device is the command byte and will be transferred to the outputs with rising edge of  $\overline{\text{CS}}$ .

#### **Over Temperature Fault**

Over temperature detect and shutdown circuits are specifically incorporated for each individual output. The shutdown following an over temperature condition is independent of the system clock, or any other logic signal. Each independent output shuts down at 155°C to 185°C. When an output shuts down due to an over temperature fault, no other outputs are affected. The MCU recognizes the fault by a one in the fault status register. After the 33880 device has cooled below the switch point temperature and 15°C hysteresis, the output will activate, unless told otherwise by the MCU via SPI to shutdown.

#### **Over Voltage Fault**

An over voltage condition on the V<sub>PWR</sub> pin will cause the device to shutdown all outputs until the over voltage condition is removed. When the over voltage condition is removed, the outputs will resume their previous state. This device does not detect an over voltage on the V<sub>DD</sub> pin. The over voltage threshold on the V<sub>PWR</sub> pin is specified as 25 to 30 V with 1.0 V typical hysteresis. A V<sub>PWR</sub> over voltage detect is *global* causing all outputs to be turned OFF.

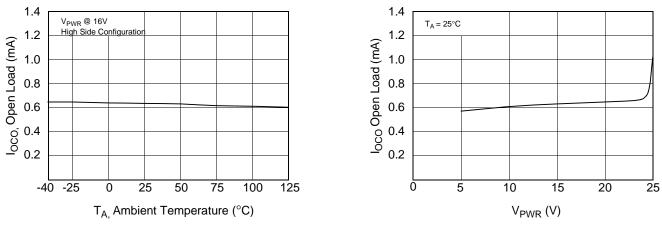

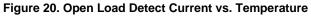

### **Output OFF Open Load Fault**

An output OFF open load fault is the detection and reporting of an *open* load when the corresponding output is disabled (input bit programmed to a logic low state). The output OFF open load fault is detected by comparing the drain-to-source voltage of the specific MOSFET output to an internally generated reference. Each output has one dedicated comparator for this purpose.

An output off open load fault is indicated when the drain-tosource voltage is less than the output threshold voltage (V<sub>THRES</sub>) of 1.0 to 3.0 V. Hence, the 33880 will declare the load *open* in the OFF state when the V<sub>DS</sub> is less than 1.0 V.

This device has an internal 650  $\mu$ A current source connected from drain to source of the output mosfet. This prevents either configuration of the driver from having a floating output. To achieve low sleep mode quiescent currents, the open load detect current source of each driver are switched off when V<sub>DD</sub> is removed.

During output switching, especially with capacitive loads, a false output OFF open load fault may be triggered. To prevent this false fault from being reported, an internal fault filter of 100 to 300  $\mu$ S is incorporated. A false fault reporting is a function of the load impedance, R<sub>DS(ON)</sub>, C<sub>OUT</sub> of the MOSFET as well as the supply voltage, V<sub>PWR</sub>. The rising edge of  $\overline{CS}$  triggers the built-in fault delay timer. The timer will time out before the fault comparator is enabled and the fault is detected. Once the

condition causing the open load fault is removed, the device will resume normal operation. The open load fault however, will be latched in the output DO register for the MCU to read.

## **Shorted Load Fault**

A shorted load (over current) fault can be caused by any output being shorted directly to supply, or an output experiencing a current greater than the current limit.

There are two safety circuits progressively in operation during load short conditions providing system protection.

- The device's output current is monitored in an analog fashion using SENSEFET<sup>™</sup> approach and current limited.

- The device's output thermal limit is sensed and when attained causes only the specific faulted output to shutdown. The output will remain off until cooled. The device will then reassert the output automatically. The cycle will continue until fault is remove or the command bit instructs the output off.

## **Under Voltage Shutdown**

An under voltage  $V_{DD}$  condition will result in the global shutdown of all outputs. The undervoltage threshold is between 3.9 V and 4.6 V. When  $V_{DD}$  goes below the threshold, all outputs are turned OFF and the Fault Status (FS) register is cleared. As  $V_{DD}$  returns to normal levels, the FS register will resume normal operation.

An under voltage condition at the V<sub>PWR</sub> pin will not cause output shutdown and reset. When V<sub>PWR</sub> is between 5.5 V and 9.0 V, the output will operate per the command word. However, the status as reported by the serial data output (DO) pin may not be accurate below 9.0 V V<sub>PWR</sub>. Proper operation at V<sub>PWR</sub> voltages below 5.5 V can not be guaranteed.

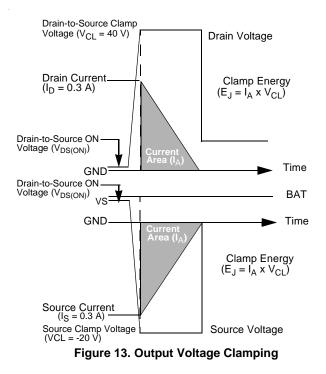

## **Output Voltage Clamp**

Each output of the 33880 incorporates an internal voltage clamp to provide fast turn-off and transient protection of each output. Each clamp independently limits the drain-to-source voltage to 45 V for low side drive configurations and -20 V for high side drive configurations. The total energy clamped (E<sub>J</sub>) can be calculated by multiplying the current area under the current curve (I<sub>A</sub>) times the clamp voltage (V<sub>CL</sub>).

Characterization of the output clamps, using a single pulse non-repetitive method at 0.3 A, indicate the maximum energy to be 50 mJ at  $150^{\circ}$ C junction temperature per output.

## **SPI Configurations**

The SPI configuration on the 33880 device is consistent with other devices in the OSS family. This device may be used in serial SPI or parallel SPI with the 33298 and 33291. Different SPI configurations may be provided. For more information, contact Motorola SMARTMOS<sup>™</sup> Analog Products Division or local Motorola representative.

## **Reverse Battery**

The 33880 has been designed with reverse battery protection on  $V_{PWR}$  pin. However, the device does not protect the load from reverse battery. During the reverse battery condition, current will flow through the load and the output MOSFET substrate diode. Under this circumstance, relays may energize and lamps will turn on. No damage will occur to the 33880. If load reverse battery protection is desired a diode must be placed in series with the load.

## **TYPICAL ELECTRICAL CHARACTERISTICS**

## **TYPICAL ELECTRICAL CHARACTERISTICS**

Figure 21. Open Load Detect Current vs. VPWR

Figure 22. Sleep State Output Leakage vs.  $V_{\text{PWR}}$

## **PACKAGE DIMENSIONS**

Figure 23. Case 751F

Figure 24. Case 1324

# NOTES:

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

MOTOROLA and the Stylized M Logo are registered in the US Patent and Trademark Office. All other product or service names are the property of their respective owners.

© Motorola, Inc. 2002

#### HOW TO REACH US:

USA/EUROPE/LOCATIONS NOT LISTED: Motorola Literature Distribution: P.O. Box 5405, Denver, Colorado 80217.

#### 1-303-675-2140 or 1-800-441-2447

JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573 Japan. 81-3-3440-3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tao Po, N.T., Hong Kong. 852-26668334

TECHNICAL INFORMATION CENTER: 1-800-521-6274

MOTOROLA

SUNSTAR 商斯达实业集团是集研发、生产、工程、销售、代理经销、技术咨询、信息服务等为一体的高科技企业,是专业高科技电子产品生产厂家,是具有10多年历史的专业电子元器件供应商,是中国最早和最大的仓储式连锁规模经营大型综合电子零部件代理分销商之一,是一家专业代理和分銷世界各大品牌IC芯片和電子元器件的连锁经营综合性国际公司,专业经营进口、国产名厂名牌电子元件,型号、种类齐全。在香港、北京、深圳、上海、西安、成都等全国主要电子市场设有直属分公司和产品展示展销窗口门市部专卖店及代理分销商,已在全国范围内建成强大统一的供货和代理分销网络。我们专业代理经销、开发生产电子元器件、集成电路、传感器、微波光电元器件、工控机/DOC/DOM 电子盘、专用电路、单片机开发、MCU/DSP/ARM/FPGA软件硬件、二极管、三极管、模块等,是您可靠的一站式现货配套供应商、方案提供商、部件功能模块开发配套商。商斯达实业公司拥有庞大的资料库,有数位毕业于著名高校——有中国电子工业摇篮之称的西安电子科技大学(西军电)并长期从事国防尖端科技研究的高级工程师为您精挑细选、量身订做各种高科技电子元器件,并解决各种技术问题。

更多产品请看本公司产品专用销售网站:

商斯达中国传感器科技信息网: http://www.sensor-ic.com/

商斯达工控安防网: <u>http://www.pc-ps.net/</u>

商斯达电子元器件网: <u>http://www.sunstare.com/</u>

商斯达微波光电产品网:HTTP://www.rfoe.net/

商斯达消费电子产品网://www.icasic.com/

商斯达实业科技产品网://www.sunstars.cn/

传感器销售热线:

地址: 深圳市福田区福华路福庆街鸿图大厦 1602 室

电话: 0755-83370250 83376489 83376549 83607652 83370251 82500323

传真: 0755-83376182 (0) 13902971329 MSN: <u>SUNS8888@hotmail.com</u>

邮编: 518033 E-mail:<u>szss20@163.com</u> QQ: 195847376

深圳赛格展销部: 深圳华强北路赛格电子市场 2583 号 电话: 0755-83665529 25059422 技术支持: 0755-83394033 13501568376

欢迎索取免费详细资料、设计指南和光盘;产品凡多,未能尽录,欢迎来电查询。 北京分公司:北京海淀区知春路132号中发电子大厦3097号

TEL: 010-81159046 82615020 13501189838 FAX: 010-62543996

- 上海分公司:上海市北京东路 668 号上海賽格电子市场 2B35 号

- TEL: 021-28311762 56703037 13701955389 FAX: 021-56703037

西安分公司:西安高新开发区 20 所(中国电子科技集团导航技术研究所)

西安劳动南路 88 号电子商城二楼 D23 号

TEL: 029-81022619 13072977981 FAX:029-88789382